### **Description**

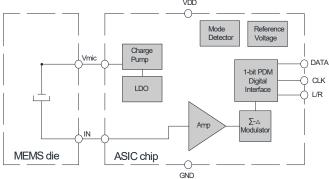

The GTD3526BA-1N is a small package, high SNR and Multimode bottom port digital MEMS microphone with 1-bit PDM output, consists of a MEMS sensor, a low noise level amplifier, and a  $\sum$ - $\triangle$  modulator.

Fig. 1 Microphone block diagram

### **Key Features**

- 3.5x2.65x0.98mm Bottom Port

- 1-bit PDM Output  $\diamondsuit$

- Narrow Sensitivity +/-1dBFS  $\diamond$

- High SNR of 65dBA  $\diamond$

- $\diamond$ LFRO <20Hz

- Flat Frequency Performance  $\diamond$

- Multi Mode(Sleep, Low power, Normal)  $\diamondsuit$

- Compatible with Standard SMD Reflow Technology  $\diamond$

- RoHS Compliance & Halogen Free

**Top View**

**Bottom View**

### **Typical Applications**

- ♦ Mobilephones

- ♦ NotebookComputers

- ♦ Smart Speakers

- ♦ Wearable Electronics

- Digital Video Cameras

- ♦ Smart Home Electronics

### **Maximum Ratings**

Stresses at the maximum ratings shown in Table 1 may cause permanent damage to the device. These are stress ratings only at which the device may not function when an operation at these or any other condition beyond those specified under "Electro-Acoustic Specifications".

**Table 1 Maximum Ratings**

| Parameters                  | Maximum Ratings | Unit          |

|-----------------------------|-----------------|---------------|

| Power supply voltage        | 6.5             | V             |

| Operation temperature range | -40~85          | ${\mathbb C}$ |

| Storage temperature range   | -40~125         | ${\mathbb C}$ |

### **Electro-Acoustic Specifications**

#### **Table 2 Normal Mode Electrical Specifications**

Test condition:  $+25\pm2^{\circ}$ C,  $60\%\sim70\%$  RH,  $86\sim106$ Kpa,  $F_{CLK}$ =2.4MHz,  $V_{DD}$ =1.8V, no load, unless otherwise noted.

| Symbol           | Description                             | Min. | Тур. | Max. | Units             |

|------------------|-----------------------------------------|------|------|------|-------------------|

| F <sub>CLK</sub> | Clock Frequency                         | 1.3  | 2.4  | 4.8  | MHz               |

| I <sub>DD</sub>  | Supply Current <sup>1</sup>             |      | 770  | 900  | uA                |

| s                | Sensitivity³, 94dB SPL@1KHz             | -27  | -26  | -25  | dBFS <sup>2</sup> |

| ΔS               | Sensitivity drop                        | <0.5 |      |      | dBFS              |

|                  | 20-5KHz Bandwidth, A-Weighted           |      | 68   |      | dB(A)             |

| SNR              | 20-8KHz Bandwidth, A-Weighted           |      | 66.5 |      | dB(A)             |

|                  | 20-20KHz Bandwidth, A-weighted          | 63   | 65   |      | dB(A)             |

|                  | 94dB SPL@1KHz                           |      | 0.15 | 0.5  | %                 |

| THD              | 115dB SPL@1KHz                          |      | 1    |      | %                 |

| AOP              | 10%THD@1KHz                             |      | 121  |      | dBSPL             |

| PSR              | Measured with 217Hz,100mVpp square wave |      | -90  | -80  | dBFS              |

| PSRR             | Measured with 1KHz,200mVpp sinewave     |      | 60   |      | dBFS              |

#### **Table 3 Low Power Mode Electrical Specifications**

Test condition:  $+25\pm2^{\circ}$ C, 60% $\sim$ 70% RH, 86 $\sim$ 106Kpa, F<sub>CLK</sub>=768KHz, V<sub>DD</sub>=1.8V, no load, unless otherwise noted.

| Symbol          | Description                              | Min. | Тур. | Max. | Units |

|-----------------|------------------------------------------|------|------|------|-------|

| FCLK            | Clock Frequency                          | 150  | 768  | 900  | KHz   |

| I <sub>DD</sub> | Supply Current                           |      | 340  | 450  | uA    |

| S               | Sensitivity, 94dB SPL@1KHz               | -27  | -26  | -25  | dBFS  |

| ΔS              | Sensitivity drop <0                      |      |      |      | dBFS  |

| SNR             | 20Hz~8KHz Bandwidth, A-weighted          |      | 64   |      | dB(A) |

|                 | 94dB SPL@1KHz                            |      | 0.15 | 0.5  | %     |

| THD             | 115dB SPL@1KHz                           |      | 1    |      | %     |

| AOP             | 10%THD@1KHz                              |      | 121  |      | dBSPL |

| PSR             | Measured with 217Hz, 100mVpp square wave |      | -90  | -80  | dBFS  |

| PSRR            | Measured with 1KHz,200mVpp sinewave      |      | 60   |      | dBFS  |

Note 1: The current consumption depends on the applied clock frequency and the load on the DATA output

Note 2: dBFS=20\*logA/B, where A is the level of signal, and B is the level that corresponds to full-scale level

Note 3: Relative to the rms level of a sine wave with positive amplitude equal to 100%1s density and Negative amplitude equal to 0% 1s density

Note 4: Frequency response, sensitivity and current consumption are tested by 100% on product line.

### **Table 4 General Electrical Specifications**

Test condition:  $+25\pm2$  °C, 60%  $\sim$  70% RH, 86~106Kpa, no load, unless otherwise noted.

| Symbol           | Description                                                                                     |                       | Min.      | Тур.      | Max.      | Units |

|------------------|-------------------------------------------------------------------------------------------------|-----------------------|-----------|-----------|-----------|-------|

| V <sub>DD</sub>  | Supply Voltage                                                                                  |                       | 1.62      | 1.8       | 3.6       | \ \   |

| ISLEEP           | Power Consumption of                                                                            | Stand By              |           | 3         | 50        | uA    |

|                  |                                                                                                 | Standby Mode          |           |           | 10        | KHz   |

| Fclk             | Clock Frequency                                                                                 | Low Power Mode        | 150       | 768       | 900       | KHz   |

|                  |                                                                                                 | Normal Mode           | 1.3       | 2.4       | 4.8       | MHz   |

| Data Format      |                                                                                                 | 1/2 Cyc               | le PDM    |           |           |       |

| Directivity      |                                                                                                 | Omni-di               | rectional |           |           |       |

| Polarity         | Increasing sound pressure                                                                       |                       | Increasi  | ng densit | ty of 1's |       |

| Isc              | Short circuit current, G                                                                        | rounded DATA          | 1         |           | 20        | mA    |

| CLOAD            | Load capacitance                                                                                |                       |           |           | 100       | pF    |

| Reset time       | Time to start up in any mode after VDD has been off for more than 10ms, while CLOCK remained on |                       |           |           | 20        | ms    |

| Start-up time    | Start-up into normal mode or LP mode                                                            |                       |           |           | 20        | ms    |

| Mode-switch time | Mode-switch Normal m mode to Normal mode                                                        | node to LP mode or LP |           |           | 20        | ms    |

#### Table 5 Digital input—output specifications

| Parameter                 | Symbol          | Min.                  | Тур. | Max.                 | Unit | Note                                                                                                  |

|---------------------------|-----------------|-----------------------|------|----------------------|------|-------------------------------------------------------------------------------------------------------|

| Clock duty cycle          |                 | 40                    | 50   | 60                   | %    |                                                                                                       |

| Operation Voltage         | $V_{DD}$        | 1.62                  |      | 3.6                  | V    |                                                                                                       |

| Input Logic Low Level     | VIL             | -0.3                  |      | 0.35×V <sub>DD</sub> | V    |                                                                                                       |

| Input Logic High Level    | V <sub>IH</sub> | 0.65×V <sub>DD</sub>  |      | V <sub>DD</sub> +0.3 | ٧    |                                                                                                       |

| Output Logic Low Level    | V <sub>OL</sub> |                       |      | 0.45                 | ٧    |                                                                                                       |

| Output Logic High Level   | V <sub>OH</sub> | V <sub>DD</sub> -0.45 |      |                      | V    |                                                                                                       |

| Clock rise time           | t <sub>CR</sub> |                       |      | 6                    | ns   | 35%~65%                                                                                               |

| Clock fall time           | t <sub>CF</sub> |                       |      | 6                    | ns   | 65%~35%                                                                                               |

| Delay time for data valid | t <sub>DV</sub> | 40                    |      | 100                  | ns   | Delay time from clock<br>edge(0.50 x VDD) to data<br>valid( <v<sub>OL or &gt; V<sub>OH</sub>)</v<sub> |

| Delay time for data driven | t <sub>DD</sub> | 25 | 50 | ns | Delay time from clock<br>edge (50% VDD) to data<br>driven.             |

|----------------------------|-----------------|----|----|----|------------------------------------------------------------------------|

| Delay time for data high Z | t <sub>Hz</sub> | 5  | 20 | ns | Delay time from clock<br>edge(50% VDD) to data<br>high impedance state |

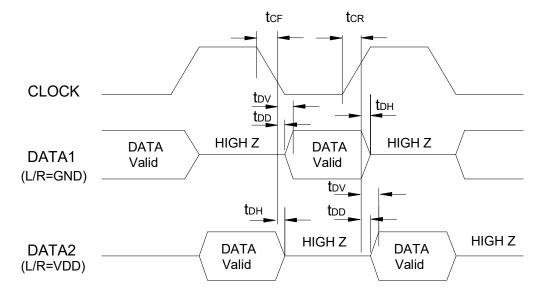

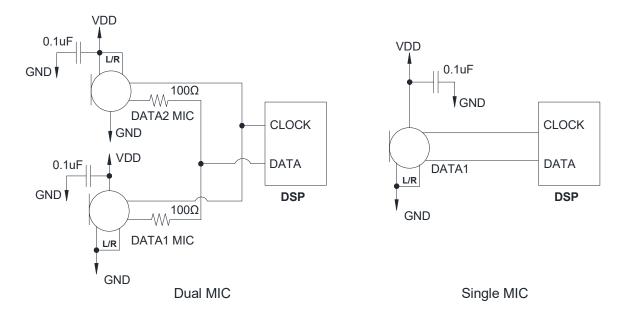

#### Table 6 L/R Channel Configuration

| Channel | L/R pad connection | DATA driven      | Data high Z      |

|---------|--------------------|------------------|------------------|

| DATA1   | GND                | CLK falling edge | CLK rising edge  |

| DATA2   | VDD                | CLK rising edge  | CLK falling edge |

Fig. 2 Recommended timing diagram

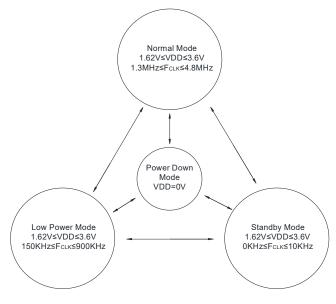

Fig. 3State diagram

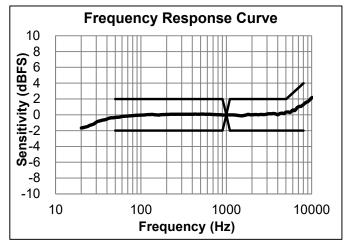

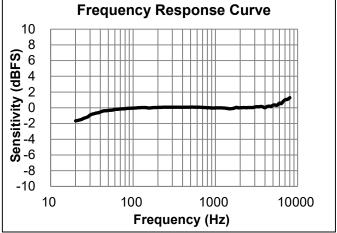

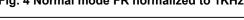

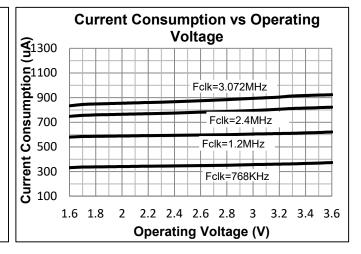

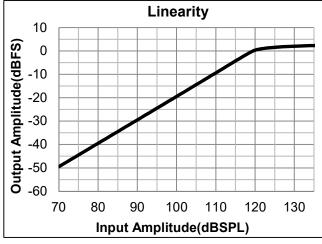

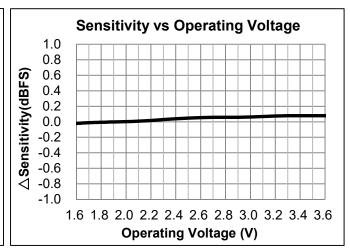

#### **Performance Curves**

All curves are tested under 1.8V, 2.4MHz unless otherwise noted.

Fig. 4 Normal mode FR normalized to 1KHz

Fig. 5 Low power mode FR normalized to 1KHz

Fig. 6 Typical THD vs Sound Pressure Level

Fig. 8 Linearity

Fig. 7 Typical Current Consumption curve

Fig. 9 Sensitivity vs Operating Voltage

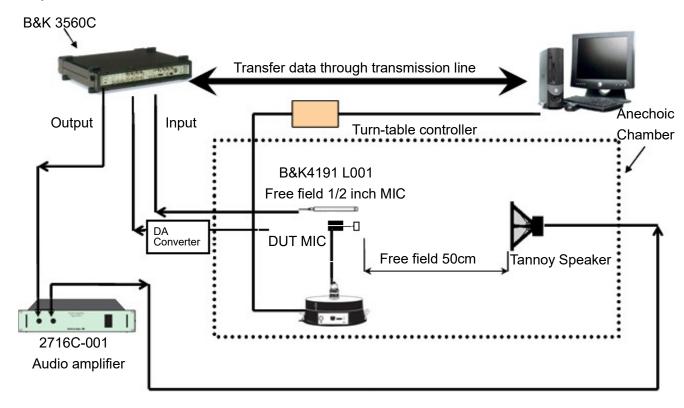

## **Measurement System Setup**

Test signal: Sinusoid, Sweep,

Step: 1/12 octave

Fig. 10 Measurement System Setup

### **Typical Application Circuit**

Fig. 11 Typical Application Circuit

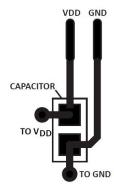

Note1: A 0.1uF ceramic type decoupling capacitor is strongly recommended for every microphone and it should be placed as close to the VDD pad to reduce the noise on power supply;

The trace connected to each pad of capacitor should be as short as possible, and should stay on one layer of PCB without via. For the best performance, recommend to place the capacitor equidistance from power and ground pins of microphone, or slightly closer to the power pin if space not allowed. System ground should connect to far side of the capacitor, as shown in fig.12.

Fig. 12 Recommended Power Supply Decoupling Capacitor Layout

Note2: Do not use a pull-up or pull-down resistor on the PDM data signal line, because it can pull the signal to an incorrect state during the period that the signal line is restarted.

Note3: When long wire is used to connect the CLK of codec and microphone, a  $50\sim100\Omega$  resistor should be placed near the codec to reduce signal over-shoot or ringing.

Note4: It is required that stereo implementations use extra data source termination resistor of  $100\Omega$ .

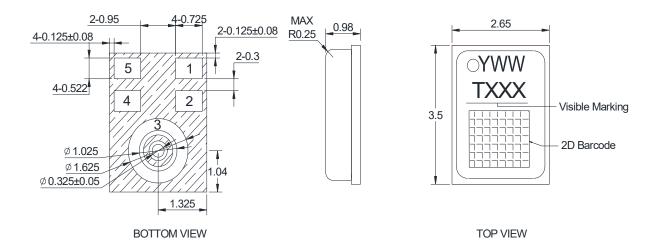

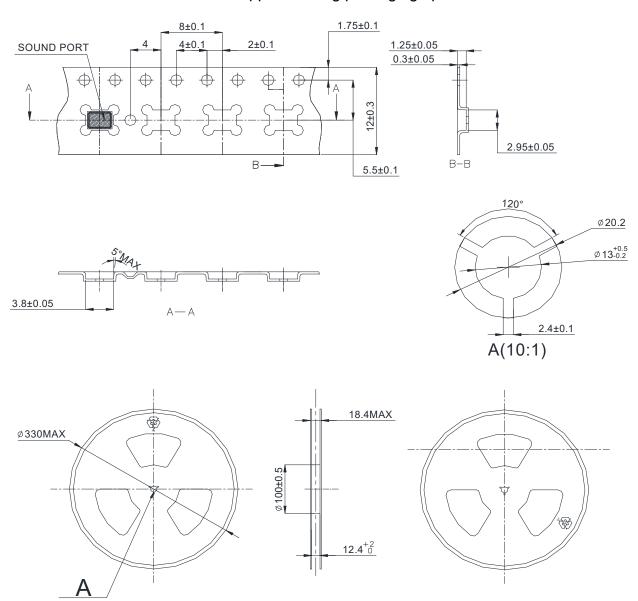

### **Mechanical Specifications**

Unit: mm Unmarked Tolerance: ± 0.1

Fig. 13 Dimension

| Item          | Dimension | Tolerance |

|---------------|-----------|-----------|

| Length        | 3.5       | ±0.1      |

| Width         | 2.65      | ±0.1      |

| Height        | 0.98      | ±0.1      |

| Acoustic Port | 0.325     | ±0.05     |

| PIN | Definition | Description                        |

|-----|------------|------------------------------------|

| 1   | DATA       | PDM output                         |

|     |            | L/R select (No internal pull-down. |

| 2   | L/R        | Must be connected to VDD or        |

|     |            | GND)                               |

| 3   | GND        | Ground                             |

| 4   | CLK        | Clock input                        |

| 5   | VDD        | Power Supply                       |

### Note:

- All Ground Pin must be connected to the ground in end application

- The L/R pin is suggested to connect to GND during single mic application.

- Identification Marking

- o: Polarity sign Y: Year WW: Week

- T: GETTOP XXX: Serial Number

- 2D Barcode

## **Reliability Specifications**

After conducting any of the following tests, the sensitivity change of DUT shall be less than ±3dBFS from its initial value unless otherwise noted, and shall keep its initial operation and appearance.

**Table 7 Electrical Specifications**

| No. | Item                                    | Test condition                                                                                                                                                                                                                             |

|-----|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Preconditioning                         | 24 hour bake at 125°C, followed by 168 hours at 85°C, 85%RH, followed by 3 passes solder reflow only for the following three tests:  High Humidity &High Heat operating Test High Humidity &High Heat operating Test Thermal Shocking Test |

| 2   | Hi-Temperature Storage Test             | 105±3℃,1000h,recover for two hours                                                                                                                                                                                                         |

| 3   | Hi-Temperature operating Test           | 105±3℃, under upper limit bias,1000h,recover for two hours                                                                                                                                                                                 |

| 4   | Low-Temperature storage Test            | -40±3°C,1000h, recover for two hours                                                                                                                                                                                                       |

| 5   | Low-Temperature operating Test          | -40±3℃, under upper limit bias,1000h,recover for two hours                                                                                                                                                                                 |

| 6   | High Humidity &High Heat operating Test | 85±3°C, 85%RH, under upper limit bias, 1000h,recover for two hours, there should be no corrosion and deformation inside of microphone after testing                                                                                        |

| 7   | High Humidity &High Heat operating Test | 65±3℃, 95%RH, under upper limit bias, 168h,recover for two hours ,there should be no corrosion and deformation inside of microphone after testing                                                                                          |

| 8   | Thermal Shocking Test                   | Double-Case Method, -40°C for 15mins→125°C for 15 mins, 100 cycles, recover for two hours                                                                                                                                                  |

| 9   | Vibration Test                          | Each 12mins for X, Y and Z axes, Frequency: 20~2000Hz, Peak Acceleration 20g, recover for two hours                                                                                                                                        |

| 10  | Drop Test                               | Height:1.5m Fixture Weight:150g (Sound Hole Diameter in the fixture is >=0.8mm) Reference Surface: slippery marble floor Duration:4 corners*4 times, 6 faces*4 times The sensitivity change should be less than 1dB after testing          |

| 11  | Tumbling Test                           | Height:1.0m Fixture Weight:150g (Sound Hole Diameter in the fixture is >=0.8mm) Duration: 300 times Recommended Time: 10-11times/Min The sensitivity change should be less than 1dB after testing                                          |

| 12 | ESD Test 1           | a. HMB Discharge Position: Charge Voltage: Discharge Network: b. CDM Discharge Position: Charge Voltage:                                                                                                                                                | I/O pins<br>±3000V<br>100pF & 1500Ω<br>I/O pins<br>±250V |  |

|----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| 13 | ESD Test 2           | The tests are performed acc<br>a. Contact Discharge<br>Discharge Position: Output of<br>Charge Voltage:±6000VDC<br>Discharge Network:150pF &<br>b. Air Discharge<br>Discharge Position: Sound F<br>Charge Voltage:±8000VDC<br>Discharge Network:150pF & | of Microphone<br>330Ω<br>Hole                            |  |

| 14 | Structure Shock Test | 10000g, Duration: 0.1ms, each 3 shocks for X/Y/Z 3 axes, The sensitivity change should be less than 1dB after testing                                                                                                                                   |                                                          |  |

| 15 | Reflow               | 3 reflow cycles with peak temperature of +260 ℃ according to reflow profile                                                                                                                                                                             |                                                          |  |

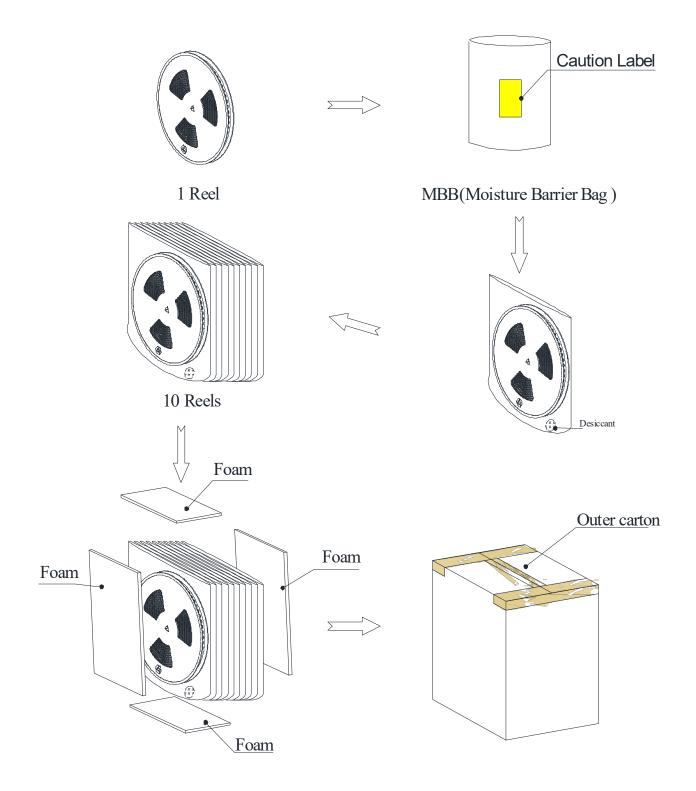

## **Packaging Details**

- \* Use ESD reel and tape for microphone packaging.

- \* Anti-static measures should be applied during packaging operation.

Fig. 14 Packaging

| Tape and Reel | φ330mm            | 5,500PCS×1=5,500PCS   |

|---------------|-------------------|-----------------------|

| Shipping Box  | 215mm*370mm*370mm | 5,500PCS×10=55,000PCS |

### **Application Design Suggestions**

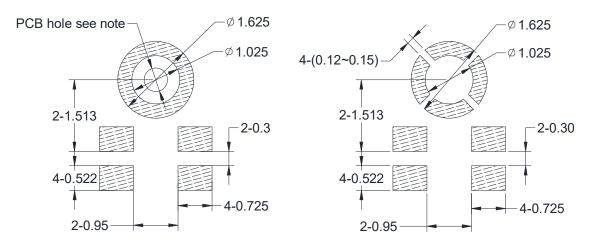

### **Recommended PCB and Stencil Design Pattern**

**Example Land Pattern**

**Example Solder Stencil Pattern**

#### Notes:

- Dimensions are in millimeters unless otherwise specified.

- Tolerance is  $\pm 0.1$ mm unless otherwise specified.

- The recommended non-plated hole diameter of PCB is 0.4-0.8mm.

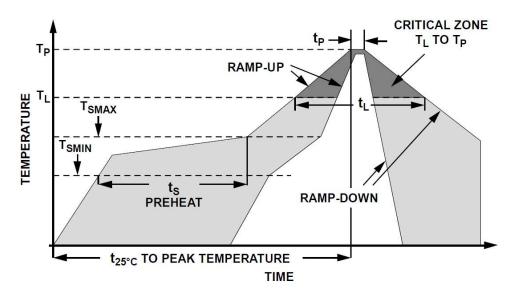

### **Temperature Profile during Reflow Process**

**Table 8 Temperature Profile during Reflow Process**

| Parameter                                   |                                             | Reference                           | Specification     |

|---------------------------------------------|---------------------------------------------|-------------------------------------|-------------------|

| Average Ramp Rate                           |                                             | T <sub>L</sub> to T <sub>P</sub>    | 3°C/sec max       |

| Preheat                                     | Minimum Temperature                         | Tsmin                               | 150°C             |

|                                             | Maximum Temperature                         | T <sub>SMAX</sub>                   | 200°C             |

|                                             | Time T <sub>SMIN</sub> to T <sub>SMAX</sub> | ts                                  | 60 sec to 180 sec |

| Ramp-Up Rate                                |                                             | T <sub>SMAX</sub> to T <sub>L</sub> | 1.25°C/sec        |

| Time Maintained Above Liquidous             |                                             | t <sub>L</sub>                      | 60 sec to 150 sec |

| Liquidous Temperature                       |                                             | TL                                  | 217°C             |

| Peak Temperature                            |                                             | T <sub>P</sub>                      | 260°C             |

| Time Within +5°C of Actual Peak Temperature |                                             | t <sub>P</sub>                      | 20 sec to 40 sec  |

| Ramp-Down Rate                              |                                             | T <sub>P</sub> to T <sub>SMAX</sub> | 6°C/sec max       |

| Time +25°C (t25°C) to Peak Temperature      |                                             |                                     | 8 min max         |

Fig. 15 Reflow Profile

#### Additional Notes:

- Mic should cool to room temp before next flow cycle if more reflow is needed.

- No more than 3 times reflow is recommended.

- Do not board wash by liquid or ultrasonic after the reflow process.

- Do not pull a vacuum over port hole of the microphone.

- Do not insert any object in port hole of device at any time.

- Suggest SMT the microphone at last time if double side PCBA used.

- Do not seal sound port during reflow .

- If there is any leakage risk, the peak temperature should be set to less than 240°C or more than 255°C.

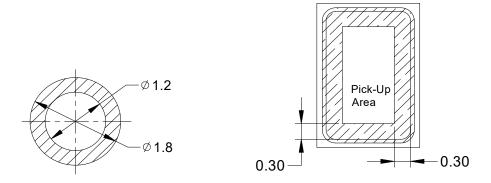

# External diameter is Φ1.8mm Inside diameter is Φ1.2mm

Fig. 16 Recommended nozzle for reflow MIC and Pick-up Area

### **Special Cautions**

#### **Air Rifle Cleaning Restriction**

Do not bring air rifle to the port hole directly.

**Recommended Condition:**

Air pressure < 0.3MPa;

Distance>5cm;

Time<5sec.

#### **Package**

Do NOT vacuum seal unused material for storage. Vacuum Sealing can cause mic damage.

#### Storage

The component needs to meet the requirement of MSL(Moisture Sensitivity Level) class 1. Please keep MICs in warehouse with humidity less than 75% and without sudden temperature change, acid air, and any other harmful air or strong magnetic field.

Please protect products against moist, shock, sunburn and pressure.

Please take proper measures against ESD in the process of assembly and transportation. Please use the shipping package for long-term storage.

#### **Discard**

For microphones to be wasted, customer shall follow the regulation of Waste Electrical and Electronic Equipment (WEEE) Directive (2002/96/EC).

Notes: More application suggestions can be found in the latest "MEMS Microphone Application Notes".

# **Specification Revisions**

| Date       | Version | Description     |

|------------|---------|-----------------|

| 01-04-2024 | V1.0    | Initial release |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |

|            |         |                 |